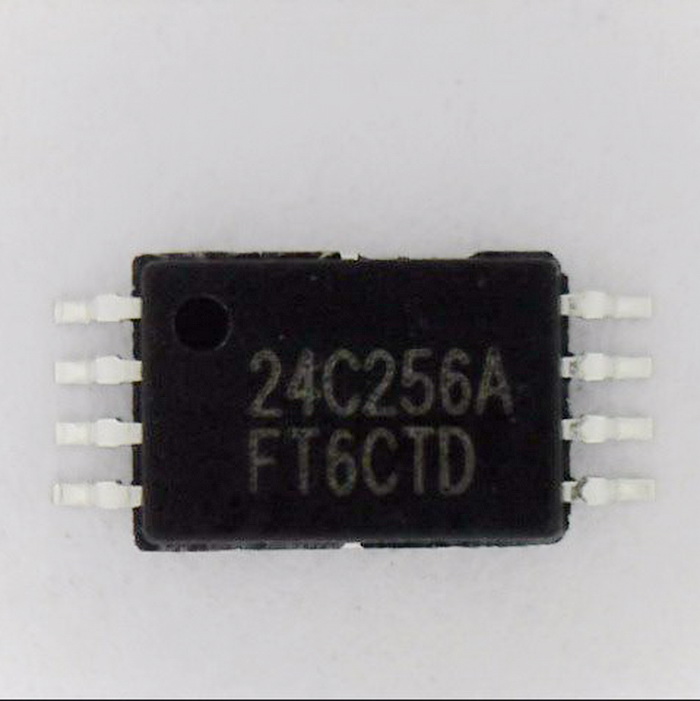

| 24C256 TSSOP |

|

零售价:¥0.53 经销商价:请登录经销商账号... |

|

单位:

无

|

|

数量:

-

+

加入购物车

直接购买

|

FEATURES

Organization:

-32K-bit x 8-bit

64-Byte page prite buffer

Two-Write serial interface

-Bi-directional data transfer protocol

Low power CMOS technology

-Active current less than 3mA (5V)

-Standby current less than 6uA (5V)

-Standby current less than 2uA (2.5V)

Wide voltage operation

-IS24C256-2: Vcc=1.8V to 5.5V

-IS24C256-3: Vcc=2.5V to 5.5V

1MHZ compatibility

Hardware data protection

-Write protect pin

Sequential read feature

Filtered inputs for noise suppression

Self time write cycle with auto clear

-5ms @ 5V

High reliability

-Endurance:100000 cycle

-Data retention:40 years

Commercial and industrial temperature ranges

9-pin PDIP,8-pin SOIC,and 14-pin TSSOP

DESCRIPTION

The IS24C256 is an electrically erasable PROM device that uses the standard 2-wire interface for communications.The IS24C256 contains a memory arry of 256k-bits (32,768 x 8),and is further subdivided into 512 pages of 64 bytes each for Page-Write mode.This EEPROM is offered in wide operating voltages of 1.8V to5.5V (is24c256-2) and2.5V to 5.5V (IS24C256-3) to be compatible with most application voltages.ISSI designed the IS24C256 to be a low-cost and low-power 2-write EEPROM solution.The devices are packaged in 8-pin PDIP,8-pin SOIC,and 14-pin TSSOP.

The IS24C256 maintains compatibility with the popular 2-wire bus protocol,so it is easy to design into applications implementing this bus type.The simple bus consists of the Serial Clock wire (SCL) and the Serial Data wire (SDA) .Using the bus,a Master device such as a microcontroller is usually connected to one or more Slave devices such as the IS24C256.The bit stream over the SDA line includes a series of bytes,which identifies a particular Slave device,an instruction,an address within that Stave device,an instruction,an address within that Slave device,and a series of data,if appropriate.The IS24C256 has a Write Protect pin (WP) to allow blocking of any write instruction transmitted over the bus.